# INTEGRATED CIRCUITS

Preliminary specification

2003 Nov 18

HILIP

## CONTENTS

| 1              | FEATURES                                               |

|----------------|--------------------------------------------------------|

| 2              | GENERAL INFORMATION                                    |

| 2.1            | DSP radio system                                       |

| 2.2            | SAA7724H                                               |

| 2.3            | Sample rates                                           |

| 3              | ORDERING INFORMATION                                   |

| 4              | BLOCK DIAGRAM                                          |

| 5              | PINNING                                                |

| 6              | FUNCTIONAL DESCRIPTION                                 |

| 6.1            | Voltage regulator                                      |

| 6.2            | Audio analog front-end                                 |

| 6.2.1          | Selector diagram                                       |

| 6.2.2          | Realization of the common mode input with AIN          |

| 6.2.3          | Realization of the differential ADIFF input            |

| 6.2.4          | Realization of the auxiliary input with volume control |

| 6.2.5          | Supplies and references                                |

| 6.3            | AD decimation paths (DAD)                              |

| 6.3.1          | LDF and AUX decimation path                            |

| 6.3.2          | ADF and audio decimation path                          |

| 6.4            | Digital audio input/output                             |

| 6.4.1          | General                                                |

| 6.4.2          | External I <sup>2</sup> S-bus input/output ports       |

| 6.4.3          | External SPDIF input                                   |

| 6.4.4          | EPICS host I <sup>2</sup> S-bus port                   |

| 6.5            | Sample rate converter                                  |

| 6.6            | IF_AD                                                  |

| 6.6.1          | IF_AD single block diagram                             |

| 6.6.2          | IF_AD detailed functional description                  |

| 6.7            | AUDIO_EPICS specific information                       |

| 6.7.1          | AUDIO_EPICS start-up                                   |

| 6.7.2          | AUDIO_EPICS memory overview                            |

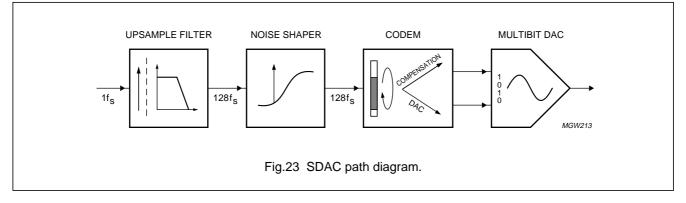

| 6.8            | SDAC output path                                       |

| 6.8.1          | DAC upsampling filter                                  |

| 6.8.2          | DAC noise shaper                                       |

| 6.8.3          | DAC CoDEM scrambler                                    |

| 6.8.4          | Multi-bit SDAC                                         |

| 6.8.5<br>6.8.6 | Analog summer function<br>SDAC application diagram     |

| 6.9            | Reset block functional overview                        |

| 6.9.1          | Asynchronous reset                                     |

| 0.0.1          | Asynomonous reset                                      |

| 6.10   | Clock circuit and oscillator                                                      |

|--------|-----------------------------------------------------------------------------------|

| 6.10.1 | Circuit description                                                               |

| 6.10.2 | External clock input mode                                                         |

| 6.10.3 | Crystal oscillator supply                                                         |

| 6.10.4 | Application guidelines                                                            |

| 6.11   | PLL circuits                                                                      |

| 6.12   | RDS                                                                               |

| 6.12.1 | General description                                                               |

| 6.12.2 | RDS I/O modes                                                                     |

| 6.12.3 | RDS demodulator                                                                   |

| 6.12.4 | RDS bit buffer                                                                    |

| 6.12.5 | RDS/RBDS decoder                                                                  |

| 7      | LIMITING VALUES                                                                   |

| 8      | THERMAL RESISTANCE                                                                |

| 9      | DC CHARACTERISTICS                                                                |

| 10     | AC CHARACTERISTICS                                                                |

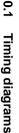

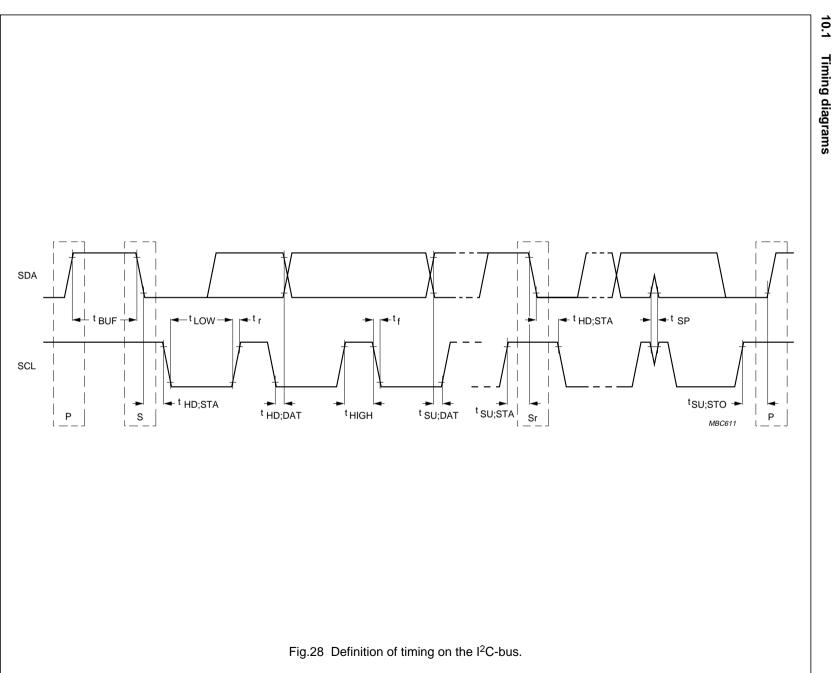

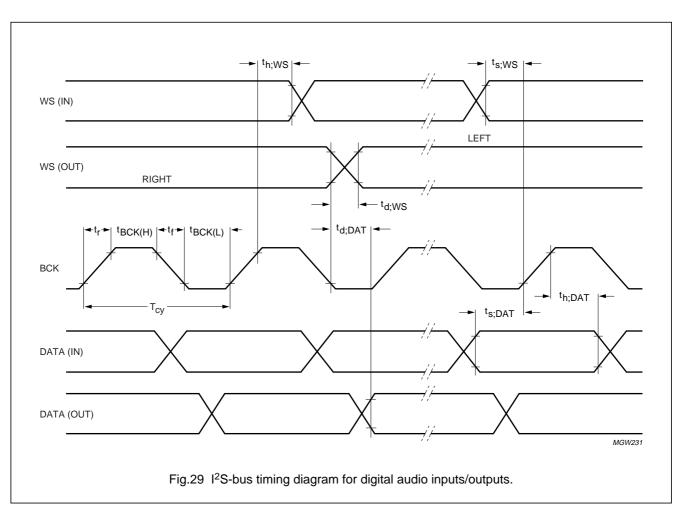

| 10.1   | Timing diagrams                                                                   |

| 11     | I <sup>2</sup> C-BUS CONTROL                                                      |

| 11.1   | I <sup>2</sup> C-bus protocol                                                     |

| 11.1.1 | Protocol of the I <sup>2</sup> C-bus commands                                     |

| 11.2   | MPI data transfer formats                                                         |

| 11.3   | Reset initialization                                                              |

| 11.4   | Defined I <sup>2</sup> C-bus address                                              |

| 11.5   | I <sup>2</sup> C-bus memory map specification                                     |

| 12     | I <sup>2</sup> S-BUS CONTROL                                                      |

| 12.1   | Basic system requirements                                                         |

| 12.2   | Serial data                                                                       |

| 12.3   | Word select                                                                       |

| 13     | PACKAGE OUTLINE                                                                   |

| 14     | SOLDERING                                                                         |

| 14.1   | Introduction to soldering surface mount                                           |

|        | packages                                                                          |

| 14.2   | Reflow soldering                                                                  |

| 14.3   | Wave soldering                                                                    |

| 14.4   | Manual soldering                                                                  |

| 14.5   | Suitability of surface mount IC packages for<br>wave and reflow soldering methods |

| 15     | DATA SHEET STATUS                                                                 |

| 16     | DEFINITIONS                                                                       |

| 17     | DISCLAIMERS                                                                       |

| 18     | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                   |

**Philips Semiconductors**

# Car radio digital signal processor

# SAA7724H

#### **1 FEATURES**

- AM and FM digitize at IF

- AM and FM narrow-band/IF AGC

- · AM and FM IF filtering

- AM and FM adjustable channel detection/variable IF

- IF filter for WX

- AM and FM demodulation

- AM and FM stereo decoding

- AM and FM stereo pilot detection

- FM pilot notch

- · AM pilot filter

- FM stereo blend, high blend, high cut, soft muting and de-emphasis

- · AM stereo blend, LP filter, high cut and soft muting

- AM and FM noise blanker

- AM and FM gain adjust and calibration (audio)

- FM multipath detection

- FM multipath correction

- Diversity switching

- Radio Data System (RDS) and Radio Broadcast Data System (RBDS) demodulation and decoding

- Tape head calibration, equalization, Dolby B and AMS (from analog tape input)

- CD gain adjust, calibration and compression (from analog or digital SPDIF/I<sup>2</sup>S-bus input)

- Parametric equalization

- Volume control

- Bass control

- Treble control

- Balance/fade control

- DC blocking filter

- Dual source select

- Dual playback

- · Channel delays

- Analog summer for four channels (through inputs MONO1 and MONO2)

- Audio limiting.

#### 1.1 Sample rates

The SAA7724H runs at a master clock of 43.2 MHz. Audio processing runs at a sample rate of

$$1 \times f_s = 42.1875 \text{ kHz} = \frac{43.2 \text{ MHZ}}{1024}$$

# SAA7724H

## 2 GENERAL INFORMATION

#### 2.1 DSP radio system

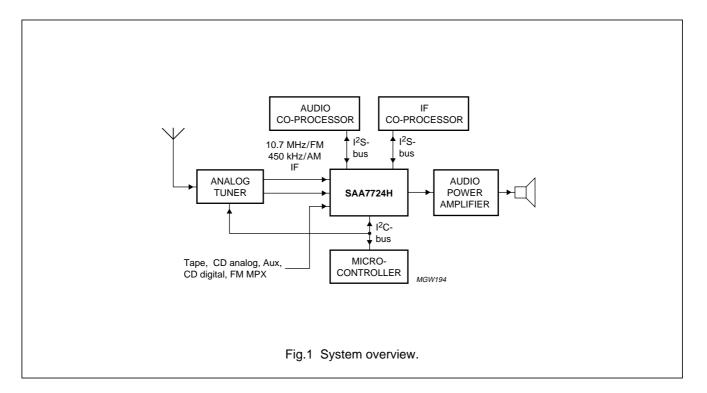

The Digital Signal Processing (DSP) radio system (see Fig.1) consists of:

- Analog tuner (also called RF/IF)

- SAA7724H

- Audio power amplifier

- Microcontroller

- IF co-processor

- Audio co-processor.

The microcontroller interfaces to the RF/IF and SAA7724H via an I<sup>2</sup>C-bus. Analog tape and CD inputs are input from other parts of the radio. The IF co-processor and audio co-processor interfaces to the SAA7724H via an I<sup>2</sup>S-bus.

## 2.2 SAA7724H

The SAA7724H digitizes up to two IF signals and performs DSP to generate left front, right front, left rear, and right rear audio and RDS/RBDS data output. The SAA7724H also samples analog baseband tape, FM MPX, AUX inputs, analog and digital CD, performs signal processing on these sampled waveforms and multiplexes the proper signal to the output. A microcontroller interface allows the SAA7724H to be controlled and monitored.

The SAA7724H is composed of hardwired and programmable DSP circuitry, with programmable parameters, such as injection frequencies, filter coefficients and control parameters. Some functions or groups of functions are implemented with programmable sequence processors.

# SAA7724H

## **3 ORDERING INFORMATION**

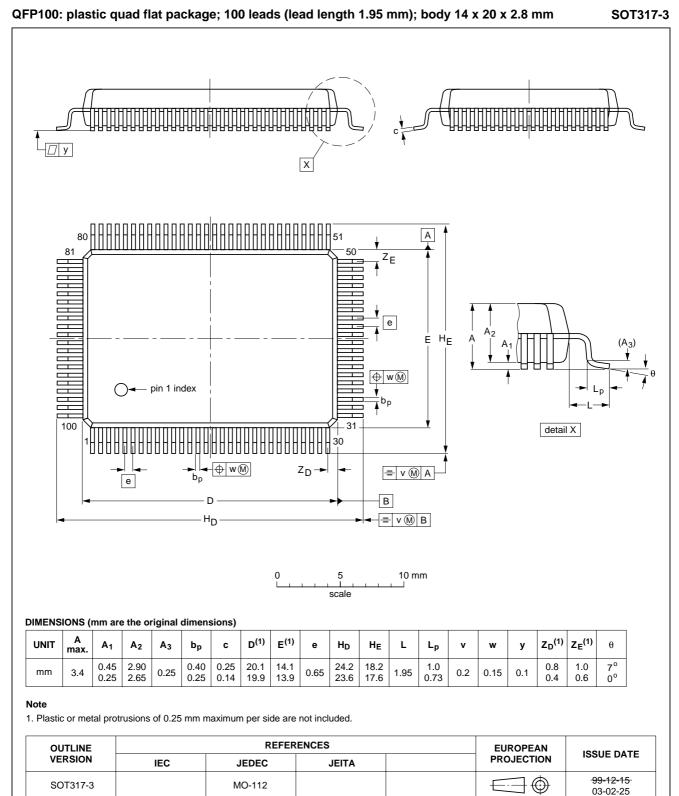

| TYPE     | PACKAGE |                                                                                               |          |  |  |  |  |  |  |

|----------|---------|-----------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|

| NUMBER   | NAME    | NAME DESCRIPTION VERSION                                                                      |          |  |  |  |  |  |  |

| SAA7724H | QFP100  | plastic quad flat package; 100 leads (lead length 1.95 mm); body $14 \times 20 \times 2.8$ mm | SOT317-3 |  |  |  |  |  |  |

# SAA7724H

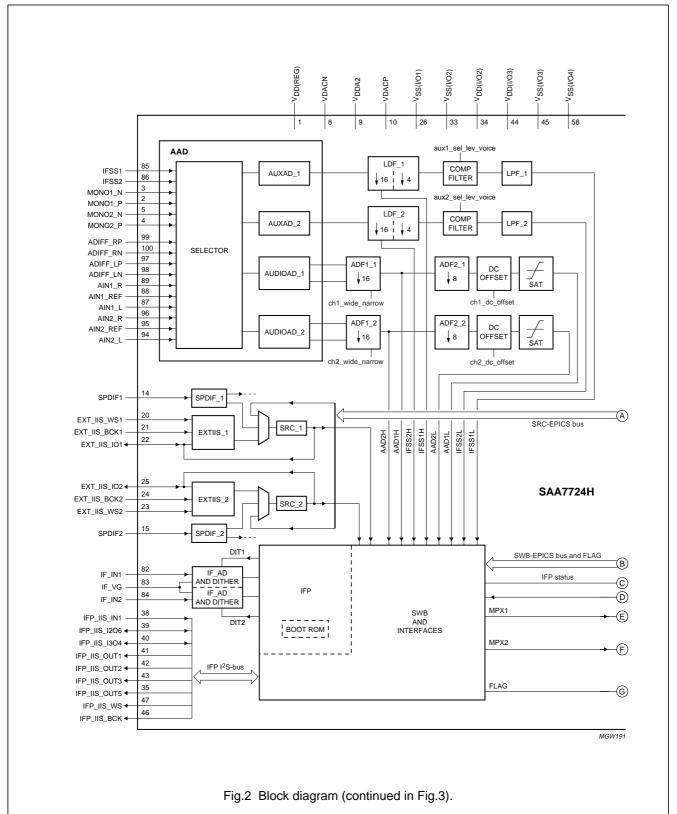

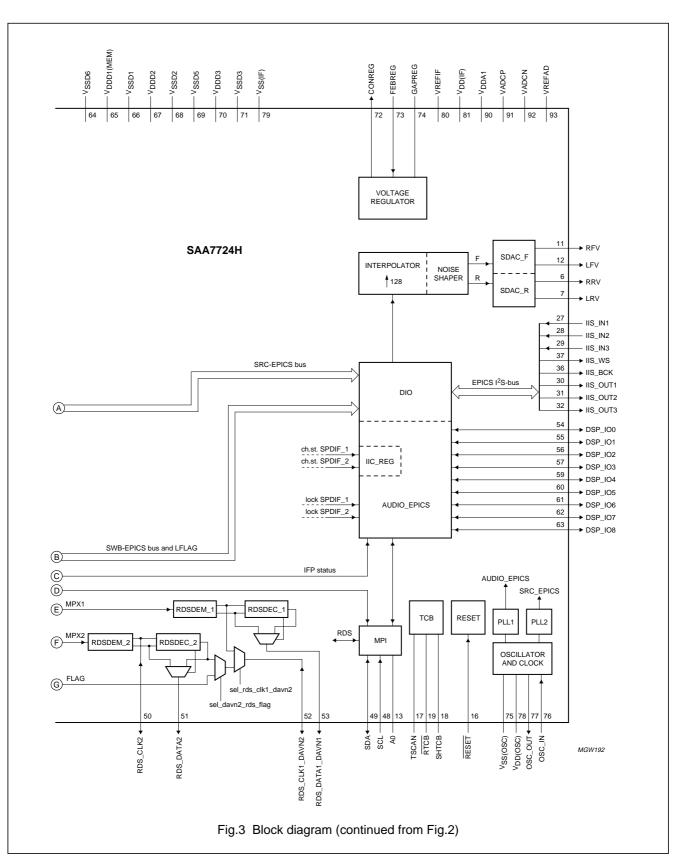

## 4 BLOCK DIAGRAM

# SAA7724H

## 5 PINNING

Table 1

Functional pin description

| SYMBOL                | DESCRIPTION |                                                                                                                                                                    |  |  |  |

|-----------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>DD(REG)</sub>  | 1           | supply voltage for 2.5 V regulator circuit and bias for ADCs (3.3 V)                                                                                               |  |  |  |

| MONO1_P               | 2           | differential positive analog input to AUX_AD2, AUDIOAD_1 and AUDIOAD_2                                                                                             |  |  |  |

| MONO1_N               | 3           | lifferential negative analog input to AUX_AD2, AUDIOAD_1 and AUDIOAD_2                                                                                             |  |  |  |

| MONO2_P               | 4           | differential positive analog input to AUX_AD2, AUDIOAD_1 and AUDIOAD_2                                                                                             |  |  |  |

| MONO2_N               | 5           | differential negative analog input to AUX_AD2, AUDIOAD_1 and AUDIOAD_2                                                                                             |  |  |  |

| RRV                   | 6           | analog audio voltage output for the right-rear speaker                                                                                                             |  |  |  |

| LRV                   | 7           | analog audio voltage output for the left-rear speaker                                                                                                              |  |  |  |

| VDACN                 | 8           | negative reference voltage for the SDAC                                                                                                                            |  |  |  |

| V <sub>DDA2</sub>     | 9           | analog supply voltage for the SDAC (2.5 V)                                                                                                                         |  |  |  |

| VDACP                 | 10          | positive reference voltage for the SDAC                                                                                                                            |  |  |  |

| RFV                   | 11          | analog audio voltage output for the right-front speaker                                                                                                            |  |  |  |

| LFV                   | 12          | analog audio voltage output for the left-front speaker                                                                                                             |  |  |  |

| A0                    | 13          | slave subaddress for I <sup>2</sup> C-bus selection                                                                                                                |  |  |  |

| SPDIF1                | 14          | SPDIF input channel 1 from digital media source                                                                                                                    |  |  |  |

| SPDIF2                | 15          | SPDIF input channel 2 from digital media source                                                                                                                    |  |  |  |

| RESET                 | 16          | reset input (active LOW)                                                                                                                                           |  |  |  |

| TSCAN                 | 17          | scan control                                                                                                                                                       |  |  |  |

| SHTCB                 | 18          | shift clock test control block                                                                                                                                     |  |  |  |

| RTCB                  | 19          | asynchronous reset test control block (active LOW)                                                                                                                 |  |  |  |

| EXT_IIS_WS1           | 20          | word select input from digital media source 1 (I <sup>2</sup> S-bus)                                                                                               |  |  |  |

| EXT_IIS_BCK1          | 21          | bit clock input from digital media source 1 (I <sup>2</sup> S-bus)                                                                                                 |  |  |  |

| EXT_IIS_IO1           | 22          | data input/output digital media source 1 (I <sup>2</sup> S-bus)                                                                                                    |  |  |  |

| EXT_IIS_WS2           | 23          | word select input from digital media source 2 (I <sup>2</sup> S-bus)                                                                                               |  |  |  |

| EXT_IIS_BCK2          | 24          | bit clock input from digital media source 2 (I <sup>2</sup> S-bus)                                                                                                 |  |  |  |

| EXT_IIS_IO2           | 25          | data input/output digital media source 2 (I <sup>2</sup> S-bus)                                                                                                    |  |  |  |

| V <sub>SS(I/O1)</sub> | 26          | ground supply 1 for external digital ports                                                                                                                         |  |  |  |

| IIS_IN1               | 27          | data channel input 1 (front channels) from external DSP IC (I <sup>2</sup> S-bus)                                                                                  |  |  |  |

| IIS_IN2               | 28          | data channel input 2 (rear channels) from external DSP IC (I <sup>2</sup> S-bus)                                                                                   |  |  |  |

| IIS_IN3               | 29          | data channel input 3 from external DSP IC (I <sup>2</sup> S-bus)                                                                                                   |  |  |  |

| IIS_OUT1              | 30          | data channel output 1 for external DSP IC activated by en_host_io (I <sup>2</sup> S-bus)                                                                           |  |  |  |

| IIS_OUT2              | 31          | data channel output 2 to external DSP IC activated by en_host_io (I <sup>2</sup> S-bus)                                                                            |  |  |  |

| IIS_OUT3              | 32          | data channel output 3 to external DSP IC activated by en_host_io (I <sup>2</sup> S-bus)                                                                            |  |  |  |

| V <sub>SS(I/O2)</sub> | 33          | ground supply 2 for external digital ports                                                                                                                         |  |  |  |

| V <sub>DD(I/O2)</sub> | 34          | supply voltage 2 for external digital ports (3.3 V)                                                                                                                |  |  |  |

| IFP_IIS_OUT5          | 35          | IFP data channel output 5 to external DSP IC activated by ifp_iis_en; can also be used as $256 \times f_s$ clock output enabled by en_256FS (I <sup>2</sup> S-bus) |  |  |  |

| IIS_BCK               | 36          | clock output for external DSP IC enabled by en_host_io (I <sup>2</sup> S-bus)                                                                                      |  |  |  |

| IIS_WS                | 37          | word select output for external DSP IC enabled by en_host_io (I <sup>2</sup> S-bus)                                                                                |  |  |  |

| IFP_IIS_IN1           | 38          | IFP data channel input 1 from external DSP IC (I <sup>2</sup> S-bus)                                                                                               |  |  |  |

| SYMBOL                 | PIN | DESCRIPTION                                                                                                                                                 |  |  |  |

|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IFP_IIS_I2O6           | 39  | IFP data channel input 2 from external DSP IC or output data channel 6 to external DSP IC selected by ifp_iis_io_mode (I <sup>2</sup> S-bus)                |  |  |  |

| IFP_IIS_I3O4           | 40  | IFP data channel input 3 from external DSP IC or output data channel 4 to external DSP IC selected by ifp_iis_io_mode (I <sup>2</sup> S-bus)                |  |  |  |

| IFP_IIS_OUT1           | 41  | IFP data channel output 1 to external DSP IC activated by ifp_iis_en (I <sup>2</sup> S-bus)                                                                 |  |  |  |

| IFP_IIS_OUT2           | 42  | IFP data channel output 2 to external DSP IC activated by ifp_iis_en (I <sup>2</sup> S-bus)                                                                 |  |  |  |

| IFP_IIS_OUT3           | 43  | IFP data channel output 3 to external DSP IC activated by ifp_iis_en (I <sup>2</sup> S-bus)                                                                 |  |  |  |

| V <sub>DD(I/O3)</sub>  | 44  | supply voltage 3 for external digital ports (3.3 V)                                                                                                         |  |  |  |

| V <sub>SS(I/O3)</sub>  | 45  | ground supply 3 for external digital ports                                                                                                                  |  |  |  |

| IFP_IIS_BCK            | 46  | IFP output clock for external DSP IC enabled by ifp_iis_en (I <sup>2</sup> S-bus)                                                                           |  |  |  |

| IFP_IIS_WS             | 47  | IFP word select output for external DSP IC enabled by ifp_iis_en (I <sup>2</sup> S-bus)                                                                     |  |  |  |

| SCL                    | 48  | serial clock input (I <sup>2</sup> C-bus)                                                                                                                   |  |  |  |

| SDA                    | 49  | serial data input/output (I <sup>2</sup> C-bus)                                                                                                             |  |  |  |

| RDS_CLK2               | 50  | RDS2 bit clock input/output; default input enabled by rds2_clkin                                                                                            |  |  |  |

| RDS_DATA2              | 51  | RDS2 data output of RDS2 demodulator                                                                                                                        |  |  |  |

| RDS_CLK1_DAVN2         | 52  | DAVN2 or RDS1 bit clock input/output; default input enabled by rds1_clkin                                                                                   |  |  |  |

| RDS_DATA1_DAVN1        | 53  | RDS1 data output of RDS1 demodulator or RDS1 decoder DAVN1                                                                                                  |  |  |  |

| DSP_IO0                | 54  | general purpose input/output for EPICS (F0 of status register)                                                                                              |  |  |  |

| DSP_IO1                | 55  | general purpose input/output for EPICS (F1 of status register)                                                                                              |  |  |  |

| DSP_IO2                | 56  | general purpose input/output for EPICS (F2 of status register)                                                                                              |  |  |  |

| DSP_IO3                | 57  | general purpose input/output for EPICS (F3 of status register)                                                                                              |  |  |  |

| V <sub>SS(I/O4)</sub>  | 58  | ground supply 4 for external digital ports                                                                                                                  |  |  |  |

| DSP_IO4                | 59  | general purpose input/output for EPICS (F4 of status register)                                                                                              |  |  |  |

| DSP_IO5                | 60  | general purpose input/output for EPICS (F5 of status register)                                                                                              |  |  |  |

| DSP_IO6                | 61  | general purpose input/output for EPICS (F6 of status register)                                                                                              |  |  |  |

| DSP_IO7                | 62  | general purpose input/output for EPICS (F7 of status register)                                                                                              |  |  |  |

| DSP_IO8                | 63  | general purpose input/output for EPICS (F8 of status register)                                                                                              |  |  |  |

| V <sub>SSD6</sub>      | 64  | ground supply for digital circuitry                                                                                                                         |  |  |  |

| V <sub>DDD1(MEM)</sub> | 65  | digital supply voltage 1 for memories (2.5 V)                                                                                                               |  |  |  |

| V <sub>SSD1</sub>      | 66  | digital ground supply 1                                                                                                                                     |  |  |  |

| V <sub>DDD2</sub>      | 67  | digital supply voltage 2 (2.5 V)                                                                                                                            |  |  |  |

| V <sub>SSD2</sub>      | 68  | digital ground supply 2                                                                                                                                     |  |  |  |

| V <sub>SSD5</sub>      | 69  | digital ground supply 5                                                                                                                                     |  |  |  |

| V <sub>DDD3</sub>      | 70  | digital supply voltage 3 (2.5 V)                                                                                                                            |  |  |  |

| V <sub>SSD3</sub>      | 71  | digital ground supply 3                                                                                                                                     |  |  |  |

| CONREG                 | 72  | 2.5 V regulator control output                                                                                                                              |  |  |  |

| FEBREG                 | 73  | 2.5 V regulator feedback input                                                                                                                              |  |  |  |

| GAPREG                 | 74  | band gap reference decoupling pin for voltage regulator                                                                                                     |  |  |  |

| V <sub>SS(OSC)</sub>   | 75  |                                                                                                                                                             |  |  |  |

| OSC_IN                 | 76  | ground supply for crystal oscillator circuitry<br>crystal oscillator input: local crystal oscillator sense for gain control or force<br>input in slave mode |  |  |  |

| SYMBOL               | PIN | DESCRIPTION                                                       |  |  |  |

|----------------------|-----|-------------------------------------------------------------------|--|--|--|

| OSC_OUT              | 77  | crystal oscillator output: drive output to crystal                |  |  |  |

| V <sub>DD(OSC)</sub> | 78  | positive supply voltage for crystal oscillator circuitry          |  |  |  |

| V <sub>SS(IF)</sub>  | 79  | IF_AD ground supply                                               |  |  |  |

| VREFIF               | 80  | IF_AD reference voltage output                                    |  |  |  |

| V <sub>DD(IF)</sub>  | 81  | IF_AD 2.5 V supply voltage                                        |  |  |  |

| IF_IN1               | 82  | analog input to IF_AD1 from tuner IF output                       |  |  |  |

| IF_VG                | 83  | IF_AD virtual ground                                              |  |  |  |

| IF_IN2               | 84  | analog input to IF_AD2 from tuner IF output                       |  |  |  |

| IFSS1                | 85  | analog IFSS1 input to AUXAD_1                                     |  |  |  |

| IFSS2                | 86  | analog IFSS2 input to AUXAD_2                                     |  |  |  |

| AIN1_L               | 87  | analog input 1 to AAD for left input buffer signal                |  |  |  |

| AIN1_REF             | 88  | common reference voltage input for AIN1 input buffer              |  |  |  |

| AIN1_R               | 89  | analog input 1 to AAD for right input buffer signal               |  |  |  |

| V <sub>DDA1</sub>    | 90  | nalog supply voltage 1 for AUXAD and AAD analog circuitry (2.5 V) |  |  |  |

| VADCP                | 91  | ositive reference voltage input for AAD                           |  |  |  |

| VADCN                | 92  | ground reference voltage input for AAD                            |  |  |  |

| VREFAD               | 93  | common mode reference voltage output for AAD, AUXAD and buffers   |  |  |  |

| AIN2_L               | 94  | analog input 2 to AAD for left input buffer signal                |  |  |  |

| AIN2_REF             | 95  | common reference voltage input for AIN2 input buffer              |  |  |  |

| AIN2_R               | 96  | analog input 2 to AAD for right input buffer signal               |  |  |  |

| ADIFF_LP             | 97  | analog input to AAD for left positive differential signal         |  |  |  |

| ADIFF_LN             | 98  | analog input to AAD for left negative differential signal         |  |  |  |

| ADIFF_RP             | 99  | analog input to AAD for right positive differential signal        |  |  |  |

| ADIFF_RN             | 100 | analog input to AAD for right negative differential signal        |  |  |  |

# Table 2 Application requirements and padcell type per pin

| SYMBOL                | PIN | DIGITAL I/O<br>LEVELS | APPLICATION<br>DIGITAL<br>FUNCTION | PIN STATE AFTER<br>RESET | HYSTERESIS<br>REQUIRED | INTERNAL<br>PULL-DOWN | CELL NAME <sup>(1)</sup> |

|-----------------------|-----|-----------------------|------------------------------------|--------------------------|------------------------|-----------------------|--------------------------|

| V <sub>DD(REG)</sub>  | 1   | -                     | -                                  | -                        | -                      | -                     | vddco                    |

| MONO1_P               | 2   | -                     | -                                  | -                        | -                      | -                     | apio                     |

| MONO1_N               | 3   | -                     | -                                  | -                        | -                      | -                     | apio                     |

| MONO2_P               | 4   | -                     | -                                  | -                        | -                      | -                     | apio                     |

| MONO2_N               | 5   | -                     | -                                  | -                        | -                      | -                     | apio                     |

| RRV                   | 6   | -                     | -                                  | -                        | -                      | -                     | apio                     |

| LRV                   | 7   | -                     | -                                  | -                        | -                      | -                     | apio                     |

| VDACN                 | 8   | -                     | -                                  | -                        | -                      | _                     | VSSCO                    |

| V <sub>DDA2</sub>     | 9   | -                     | -                                  | -                        | -                      | -                     | vddco                    |

| VDACP                 | 10  | -                     | -                                  | -                        | -                      | -                     | vddco                    |

| RFV                   | 11  | -                     | -                                  | -                        | -                      | _                     | apio                     |

| LFV                   | 12  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| A0                    | 13  | 0 to 5 V DC tolerant  | input                              | -                        | yes                    | pull-down             | ipthdt5v                 |

| SPDIF1                | 14  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| SPDIF2                | 15  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| RESET                 | 16  | 0 to 5 V DC tolerant  | input                              | input                    | yes                    | pull-down             | ipthdt5v                 |

| TSCAN                 | 17  | 0 to 5 V DC tolerant  | input                              | input                    | yes                    | pull-down             | ipthdt5v                 |

| SHTCB                 | 18  | 0 to 5 V DC tolerant  | input                              | input                    | yes                    | pull-down             | ipthdt5v                 |

| RTCB                  | 19  | 0 to 5 V DC tolerant  | input                              | input                    | yes                    | pull-down             | ipthdt5v                 |

| EXT_IIS_WS1           | 20  | 0 to 5 V DC tolerant  | input                              | input                    | yes                    | pull-down             | ipthdt5v                 |

| EXT_IIS_BCK1          | 21  | 0 to 5 V DC tolerant  | input                              | input                    | yes                    | pull-down             | ipthdt5v                 |

| EXT_IIS_IO1           | 22  | 0 to 5 V DC tolerant  | bi-directional                     | input                    | yes                    | pull-down             | bpts10tht5v              |

| EXT_IIS_WS2           | 23  | 0 to 5 V DC tolerant  | input                              | input                    | yes                    | pull-down             | ipthdt5v                 |

| EXT_IIS_BCK2          | 24  | 0 to 5 V DC tolerant  | input                              | input                    | yes                    | pull-down             | ipthdt5v                 |

| EXT_IIS_IO2           | 25  | 0 to 5 V DC tolerant  | bi-directional                     | input                    | yes                    | pull-down             | bpts10tht5v              |

| V <sub>SS(I/O1)</sub> | 26  | _                     | -                                  | _                        | -                      | -                     | vsse3v3                  |

| IIS_IN1               | 27  | 0 to 3.3 V DC         | input                              | input                    | yes                    | pull-down             | bpt4mthd                 |

| IIS_IN2               | 28  | 0 to 3.3 V DC         | input                              | input                    | yes                    | pull-down             | bpt4mthd                 |

| IIS_IN3               | 29  | 0 to 3.3 V DC         | input                              | input                    | yes                    | pull-down             | bpt4mthd                 |

Car radio digital signal processor

\_

2003 Nov 18

Preliminary specification

2003 Nov 18

\_

| SYMBOL                | PIN | DIGITAL I/O<br>LEVELS | APPLICATION<br>DIGITAL<br>FUNCTION | PIN STATE AFTER<br>RESET                      | HYSTERESIS<br>REQUIRED | INTERNAL<br>PULL-DOWN | CELL NAME <sup>(1)</sup> |

|-----------------------|-----|-----------------------|------------------------------------|-----------------------------------------------|------------------------|-----------------------|--------------------------|

| IIS_OUT1              | 30  | 0 to 3.3 V DC         | output                             | output and LOW level                          | -                      | -                     | ops10c                   |

| IIS_OUT2              | 31  | 0 to 3.3 V DC         | output                             | output and LOW level                          | -                      | -                     | ops10c                   |

| IIS_OUT3              | 32  | 0 to 3.3 V DC         | output                             | output and LOW level                          | -                      | -                     | ops10c                   |

| V <sub>SS(I/O2)</sub> | 33  | -                     | _                                  | -                                             | -                      | _                     | vsse3v3                  |

| V <sub>DD(I/O2)</sub> | 34  | -                     | -                                  | -                                             | -                      | -                     | vdde3v3                  |

| IFP_IIS_OUT5          | 35  | 0 to 3.3 V DC         | output                             | output and LOW level                          | -                      | -                     | ops10c                   |

| IIS_BCK               | 36  | 0 to 3.3 V DC         | output                             | 3-state                                       | _                      | _                     | ot4mc                    |

| IIS_WS                | 37  | 0 to 3.3 V DC         | output                             | 3-state                                       | _                      | _                     | ots10c                   |

| IFP_IIS_IN1           | 38  | 0 to 3.3 V DC         | input                              | input                                         | yes                    | pull-down             | ipthd                    |

| IFP_IIS_I2O6          | 39  | 0 to 3.3 V DC         | bi-directional                     | input                                         | yes                    | pull-down             | bpts10thd                |

| IFP_IIS_I3O4          | 40  | 0 to 3.3 V DC         | bi-directional                     | input                                         | yes                    | pull-down             | bpts10thd                |

| IFP_IIS_OUT1          | 41  | 0 to 3.3 V DC         | output                             | output and LOW level                          | -                      | -                     | ops10c                   |

| IFP_IIS_OUT2          | 42  | 0 to 3.3 V DC         | output                             | output and LOW level                          | _                      | _                     | ops10c                   |

| IFP_IIS_OUT3          | 43  | 0 to 3.3 V DC         | output                             | output and LOW level                          | _                      | _                     | ops10c                   |

| V <sub>DD(I/O3)</sub> | 44  | -                     | -                                  | -                                             | -                      | -                     | vdde3v3                  |

| V <sub>SS(I/O3)</sub> | 45  | _                     | _                                  | _                                             | _                      | _                     | vsse3v3                  |

| IFP_IIS_BCK           | 46  | 0 to 3.3 V DC         | output                             | 3-state                                       | _                      | _                     | ot4mc                    |

| IFP_IIS_WS            | 47  | 0 to 3.3 V DC         | output                             | 3-state                                       | -                      | -                     | ots10c                   |

| SCL                   | 48  | 0 to 5 V DC tolerant  | input                              | input                                         | yes                    | _                     | iptht5v                  |

| SDA                   | 49  | 0 to 5 V DC tolerant  | bi-directional                     | input                                         | _                      | _                     | iic400kt5v               |

| RDS_CLK2              | 50  | 0 to 5 V DC tolerant  | bi-directional                     | input                                         | yes                    | -                     | bptons10tht5v            |

| RDS_DATA2             | 51  | 0 to 5 V DC tolerant  | output                             | output mode<br>(level depends on<br>RDS data) | -                      | -                     | bptons10tht5v            |

| RDS_CLK1_DAVN2        | 52  | 0 to 5 V DC tolerant  | bi-directional                     | input                                         | yes                    |                       | bptons10tht5v            |

| RDS_DATA1_DAVN1       | 53  | 0 to 5 V DC tolerant  | output                             | output mode<br>(level depends on<br>RDS data) | -                      | -                     | bptons10tht5v            |

| DSP_IO0               | 54  | 0 to 5 V DC tolerant  | bi-directional                     | input                                         | yes                    | _                     | bptons10tht5v            |

| DSP_IO1               | 55  | 0 to 5 V DC tolerant  | bi-directional                     | input                                         | yes                    | _                     | bptons10tht5v            |

| DSP_IO2               | 56  | 0 to 5 V DC tolerant  | bi-directional                     | input                                         | yes                    | -                     | bptons10tht5v            |

Car radio digital signal processor

SAA7724H

12

2003 Nov 18

\_

| SYMBOL                 | PIN | DIGITAL I/O<br>LEVELS | APPLICATION<br>DIGITAL<br>FUNCTION | PIN STATE AFTER<br>RESET | HYSTERESIS<br>REQUIRED | INTERNAL<br>PULL-DOWN | CELL NAME <sup>(1)</sup> |

|------------------------|-----|-----------------------|------------------------------------|--------------------------|------------------------|-----------------------|--------------------------|

| DSP_IO3                | 57  | 0 to 5 V DC tolerant  | bi-directional                     | input                    | yes                    | _                     | bptons10tht5v            |

| V <sub>SS(I/O4)</sub>  | 58  | -                     | -                                  | -                        | _                      | -                     | vsse3v3                  |

| DSP_IO4                | 59  | 0 to 5 V DC tolerant  | bi-directional                     | input                    | yes                    | -                     | bptons10tht5v            |

| DSP_IO5                | 60  | 0 to 5 V DC tolerant  | bi-directional                     | input                    | yes                    | _                     | bptons10tht5v            |

| DSP_IO6                | 61  | 0 to 5 V DC tolerant  | bi-directional                     | input                    | yes                    | _                     | bptons10tht5v            |

| DSP_IO7                | 62  | 0 to 5 V DC tolerant  | bi-directional                     | input                    | yes                    | -                     | bptons10tht5v            |

| DSP_IO8                | 63  | 0 to 5 V DC tolerant  | bi-directional                     | input                    | yes                    | _                     | bptons10tht5v            |

| V <sub>SSD6</sub>      | 64  | _                     | _                                  | _                        | _                      | _                     | vssis                    |

| V <sub>DDD1(MEM)</sub> | 65  | -                     | _                                  | -                        | -                      | _                     | vddco                    |

| V <sub>SSD1</sub>      | 66  | _                     | _                                  | _                        | _                      | _                     | vssis                    |

| V <sub>DDD2</sub>      | 67  | _                     | _                                  | _                        | _                      | _                     | vddi                     |

| V <sub>SSD2</sub>      | 68  | _                     | _                                  | _                        | _                      | _                     | vssis                    |

| V <sub>SSD5</sub>      | 69  | _                     | _                                  | _                        | _                      | -                     | vssis                    |

| V <sub>DDD3</sub>      | 70  | _                     | _                                  | _                        | _                      | -                     | vddi                     |

| V <sub>SSD3</sub>      | 71  | _                     | _                                  | _                        | _                      | -                     | vssis                    |

| CONREG                 | 72  | _                     | _                                  | _                        | _                      | -                     | apio                     |

| FEBREG                 | 73  | _                     | _                                  | _                        | _                      | -                     | apio                     |

| GAPREG                 | 74  | _                     | _                                  | _                        | _                      | _                     | apio                     |

| V <sub>SS(OSC)</sub>   | 75  | _                     | _                                  | _                        | _                      | -                     | vssco                    |

| OSC_IN                 | 76  | _                     | _                                  | _                        | _                      | -                     | apio                     |

| OSC_OUT                | 77  | _                     | _                                  | _                        | _                      | _                     | apio                     |

| V <sub>DD(OSC)</sub>   | 78  | _                     | _                                  | _                        | _                      | -                     | vddco                    |

| V <sub>SS(IF)</sub>    | 79  | _                     | _                                  | _                        | _                      | -                     | vssco                    |

| VREFIF                 | 80  | -                     | _                                  | _                        | -                      | _                     | apio                     |

| V <sub>DD(IF)</sub>    | 81  | _                     | _                                  | _                        | -                      | _                     | vddco                    |

| IF_IN1                 | 82  | -                     | _                                  | _                        | -                      | _                     | aprf                     |

| IF_VG                  | 83  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| IF_IN2                 | 84  | -                     | _                                  | _                        | -                      | _                     | aprf                     |

| IFSS1                  | 85  | -                     | _                                  | _                        | -                      | _                     | apio                     |

| IFSS2                  | 86  | _                     | _                                  | _                        | _                      | _                     | apio                     |

# Car radio digital signal processor

SAA7724H

Preliminary specification

$\frac{1}{\omega}$

2003 Nov 18

\_

| SYMBOL            | PIN | DIGITAL I/O<br>LEVELS | APPLICATION<br>DIGITAL<br>FUNCTION | PIN STATE AFTER<br>RESET | HYSTERESIS<br>REQUIRED | INTERNAL<br>PULL-DOWN | CELL NAME <sup>(1)</sup> |

|-------------------|-----|-----------------------|------------------------------------|--------------------------|------------------------|-----------------------|--------------------------|

| AIN1_L            | 87  | -                     | _                                  | -                        | -                      | -                     | apio                     |

| AIN1_REF          | 88  | -                     | _                                  | _                        | -                      | -                     | apio                     |

| AIN1_R            | 89  | -                     | -                                  | _                        | -                      | -                     | apio                     |

| V <sub>DDA1</sub> | 90  | -                     | -                                  | -                        | -                      | -                     | vddco                    |

| VADCP             | 91  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| VADCN             | 92  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| VREFAD            | 93  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| AIN2_L            | 94  | -                     | -                                  | _                        | -                      | -                     | apio                     |

| AIN2_REF          | 95  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| AIN2_R            | 96  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| ADIFF_LP          | 97  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| ADIFF_LN          | 98  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| ADIFF_RP          | 99  | -                     | -                                  | -                        | -                      | -                     | apio                     |

| ADIFF_RN          | 100 | -                     | -                                  | _                        | -                      | -                     | apio                     |

Note

1. See Table 3.

Preliminary specification

Car radio digital signal processor

Philips Semiconductors

# SAA7724H

| PADCELL<br>NAME | LIBRARY NAME                                                                           | FUNCTIONAL SPECIFICATION                                                                        |  |  |

|-----------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|

| Inputs          |                                                                                        |                                                                                                 |  |  |

| ipthd           | iolib_nlm                                                                              | input pad; hysteresis; pull-down; TTL levels                                                    |  |  |

| iptht5v         | iolib_nlm_danger                                                                       | input pad; hysteresis; TTL levels; 5 V tolerant                                                 |  |  |

| ipthdt5v        | iolib_nlm_danger                                                                       | input pad; hysteresis; pull-down; TTL levels; 5 V tolerant                                      |  |  |

| Outputs         |                                                                                        |                                                                                                 |  |  |

| ot4mc           | iolib_nIm                                                                              | output; 3-state; 4 mA                                                                           |  |  |

| ops10c          | iolib_nlm                                                                              | output plain; 10 ns slew rate                                                                   |  |  |

| ots10c          | iolib_nlm                                                                              | output; 3-state; 10 ns slew rate                                                                |  |  |

| l/Os            |                                                                                        |                                                                                                 |  |  |

| iic400kt5v      | iolib_nlm_danger input/output; 400 kHz I <sup>2</sup> C-bus special cell; 5 V tolerant |                                                                                                 |  |  |

| bpt4mthd        | iolib_nlm                                                                              | input/output; 4 mA; hysteresis; pull-down; TTL input levels                                     |  |  |

| bpts10thd       | iolib_nlm                                                                              | input/output; 10 ns slew rate; hysteresis; pull-down; TTL input levels                          |  |  |

| bpts10tht5v     | iolib_nlm_danger                                                                       | input/output; 10 ns slew rate; hysteresis; TTL input levels; 5 V tolerant                       |  |  |

| bptons10tht5v   | iolib_nlm_danger                                                                       | input/output; open-drain N-channel; 10 ns slew rate; hysteresis; TTL input levels; 5 V tolerant |  |  |

| Special         |                                                                                        |                                                                                                 |  |  |

| apio            | iolib_nlm                                                                              | analog pad input or output                                                                      |  |  |

| aprf            | iolib_nlm                                                                              | analog high frequency pad input or output                                                       |  |  |

| Supply          |                                                                                        |                                                                                                 |  |  |

| vddco           | iolib_nlm                                                                              | V <sub>DD</sub> core only supply; not connected to internal supply ring                         |  |  |

| VSSCO           | iolib_nlm                                                                              | V <sub>SS</sub> core only supply; not connected to internal supply ring                         |  |  |

| vddi            | iolib_nlm                                                                              | V <sub>DD</sub> core supply; connected to internal supply ring                                  |  |  |

| vssis           | iolib_nlm                                                                              | V <sub>SS</sub> core supply; connected to internal supply ring and substrate                    |  |  |

| vdde3v3         | iolib_nlm                                                                              | V <sub>DD</sub> supply peripheral only                                                          |  |  |

| vsse3v3         | iolib_nlm                                                                              | V <sub>SS</sub> supply peripheral only                                                          |  |  |

#### - I. I ... - -... . . . .. . **م** م

#### Notes

- 1. All pull-down inputs or disabled I/Os with pull-down, may be left open-circuit. Internally the logic level is guaranteed LOW, but the pull-down doesn't behave as a normal resistor seen at the pin itself.

- 2. 5 V tolerant means that the input or 3-stated/disabled output is functioning correctly and will not be damaged when applying externally 5 V, and can thus be used in a normal application. The tolerances of the 5 V are given in the limiting values; see Chapter 7.

SAA7724H

## 6 FUNCTIONAL DESCRIPTION

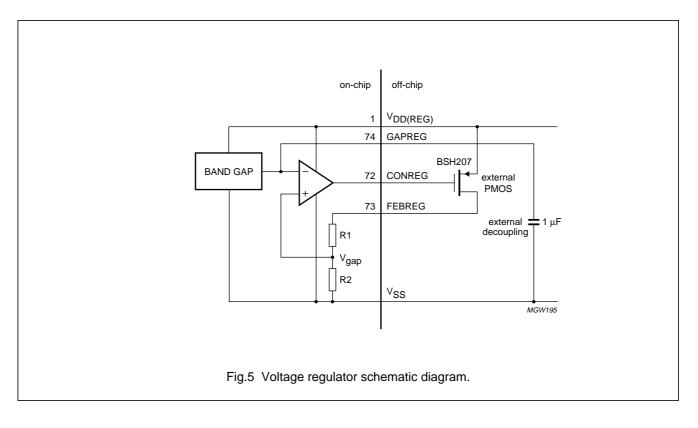

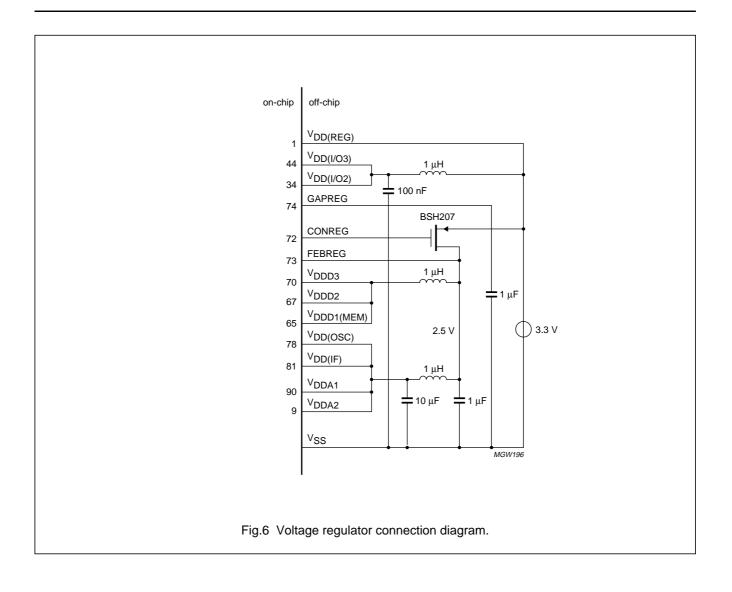

#### 6.1 Voltage regulator

A voltage regulator (see Fig.5) controls all 2.5 V supplies of the chip (see Fig.6). The input supply voltage is 3.3 V. An external PMOS power transistor (e.g. BSH207) is used to handle power. The regulated 2.5 V supply is derived from a band gap voltage, which is AC-decoupled by an external capacitor.

SAA7724H

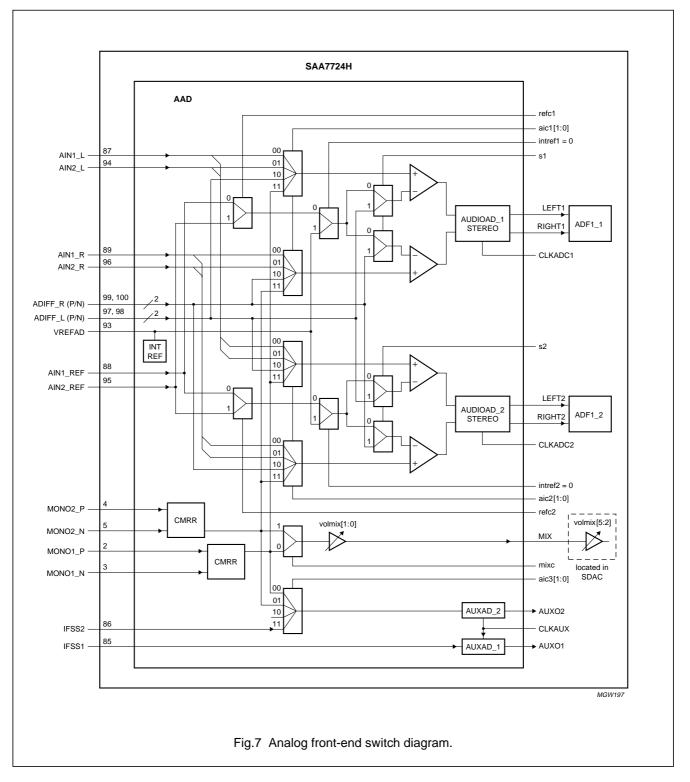

#### 6.2 Audio analog front-end

The analog front-end consists of two identical 3rd-order sigma delta stereo ADCs (ADC1 and ADC2) with several input control blocks for handling common mode signals and acting as input selector (see Fig.7).

# SAA7724H

The inputs ADIFF, AIN1, AIN2, MONO1 and MONO2 can be selected with the audio input controls (aic1 and aic2). The ground reference (REF1 and REF2) can be selected (refc1 and refc2) to enable the handling of common mode signals for AIN1 and AIN2. The switches s1 and s2 are needed for handling fully differential inputs at the ADIFF pins.

The MONO1 and MONO2 inputs have their own CMRR input stage and can be redirected to ADC1 and/or ADC2 via the audio input control (aic1 and aic2). In this event, the ground reference should be switched to internal (intref = 1). It is also possible to pass MONO1/MONO2 to

the AUXAD (controlled by aic3) or directly mix the same MONO input with four DAC output channels, incorporating volume control.

#### 6.2.1 SELECTOR DIAGRAM

Three bits are available to make it possible to redirect the inputs with their corresponding reference to the required AUDIOAD (see Tables 4 and 5). The input control for the AUXAD\_2 is given in Table 6. The input selection of the mixer is given in Table 7.

| Table 4 | Reference connection for AUDIOAD_1 and AUDIOAD_2 |  |

|---------|--------------------------------------------------|--|

|---------|--------------------------------------------------|--|

| I <sup>2</sup> C-BUS BIT |                  |        | REFERENCE CONNECTION FOR |  |

|--------------------------|------------------|--------|--------------------------|--|

| refc1, refc2             | intref1, intref2 | s1, s2 | AUDIOAD_1 and AUDIOAD_2  |  |

| 0                        | 0                | 0      | REF1                     |  |

| 1                        | 0                | 0      | REF2                     |  |

| _                        | 1                | 0      | VREFAD                   |  |

| _                        | -                | 1      | differential             |  |

Table 5

Input connection for AUDIOAD\_1 and AUDIOAD\_2

| I <sup>2</sup> C-BUS BIT |                  | PREFERRED REFERENCE | INPUT CONNECTION FOR    |  |

|--------------------------|------------------|---------------------|-------------------------|--|

| aic1[1], aic2[1]         | aic1[0], aic2[0] | FREFERRED REFERENCE | AUDIOAD_1 and AUDIOAD_2 |  |

| 0                        | 0                | REF1                | AIN1                    |  |

| 0                        | 1                | REF2                | AIN2                    |  |

| 1                        | 0                | differential        | ADIFF                   |  |

| 1                        | 1                | VREFAD              | MONO1 and MONO2         |  |

Table 6 Input connection for AUXAD\_2

| I <sup>2</sup> C-BUS BIT |         |                              |  |  |

|--------------------------|---------|------------------------------|--|--|

| aic3[1]                  | aic3[0] | INPUT CONNECTION FOR AUXAD_2 |  |  |

| 0                        | 0       | MONO1                        |  |  |

| 0                        | 1       | MONO2                        |  |  |

| 1                        | 0       | not connected                |  |  |

| 1                        | 1       | IFSS2                        |  |  |

#### Table 7 Input connection for the MIXER

| I <sup>2</sup> C-BUS BIT | INPUT CONNECTION FOR THE MIXER |  |

|--------------------------|--------------------------------|--|

| mixc                     | INFOT CONNECTION FOR THE MIXER |  |

| 0                        | MONO1                          |  |

| 1                        | MONO2                          |  |

# SAA7724H

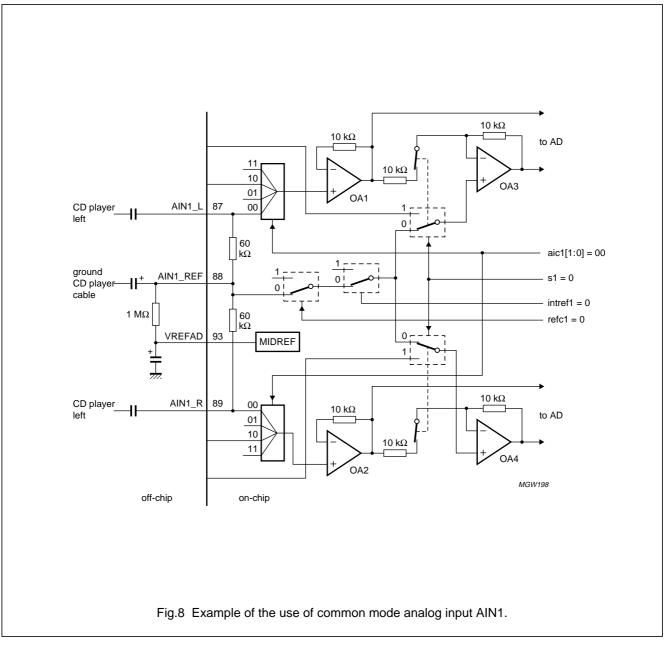

# 6.2.2 REALIZATION OF THE COMMON MODE INPUT WITH AIN

A high CMRR can be created by the use of REF1 and REF2. These pins can be connected to the positive input of the second operational amplifier in the signal path with bits intref1, intref2, refc1 and refc2 (see Fig.8). The signal (of which a high CMRR is required) has a signal and a common signal as input. The common signal is connected to pin REF1 and/or REF2 and can be selected with bits refc1 and/or refc2.

The actual input can be selected with the audio input control (bits aic1[1:0] and aic2[1:0]). In Fig.8 the AIN1 input is selected. In this situation both signal lines going to the ADC will contain the common mode signal. The ADC itself will suppress this common mode signal with a high rejection ratio.

The input pins AIN1\_L and AIN1\_R are connected directly to the source. The 1 M $\Omega$  resistor provides the DC biasing of OA3 and OA4. The impedance level, in combination with the parasitic capacitance at input pin AIN\_L or AIN\_R, greatly determines the achievable common rejection ratio.

# SAA7724H

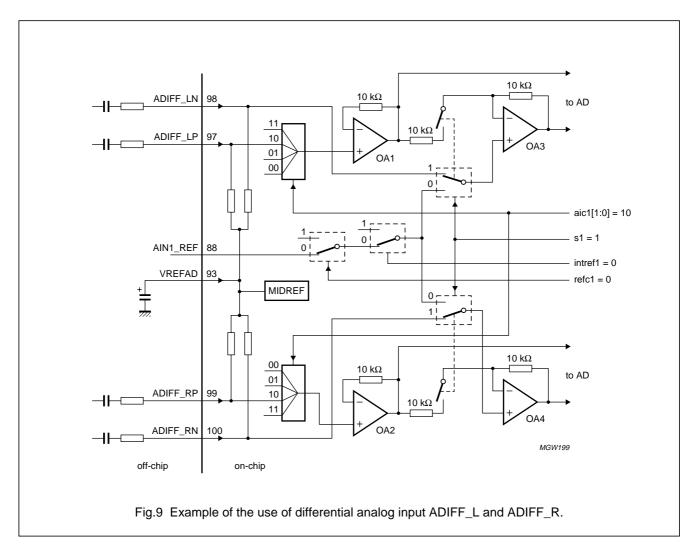

#### 6.2.3 REALIZATION OF THE DIFFERENTIAL ADIFF INPUT

The ADIFF input is fully differential. The signal that is connected to this input should be a symmetrical signal.

Besides bits aic1[1:0] and aic2[1:0], to select the ADIFF\_L and ADIFF\_R input, the switches s1 and s2 are needed to put the ADIFF\_L and ADIFF\_R inputs in true differential mode (see Fig.9).

SAA7724H

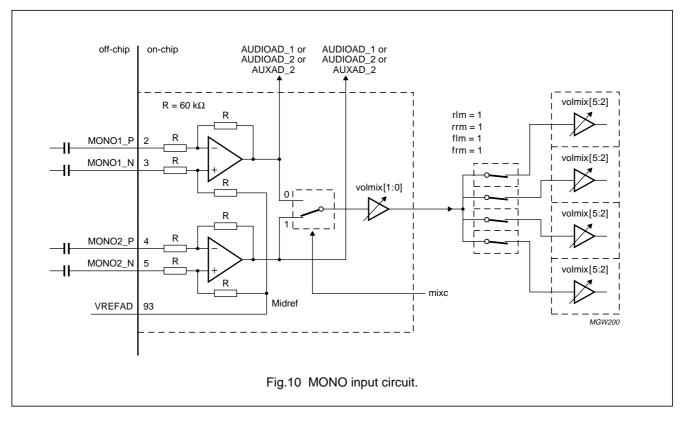

# 6.2.4 REALIZATION OF THE AUXILIARY INPUT WITH VOLUME CONTROL

A common mode input with volume control for mixing with four DAC outputs is provided (see Fig.10). The inputs consist of pins MONO1\_P and MONO2\_P, both accompanied with their ground signals (pins MONO1\_N and MONO2\_N). After selection of MONO1 or MONO2, with bit mixc, the volume can be changed from 0 to -22.5 dB in 1.5 dB steps. The attenuated signal can be added to the left and/or right front and/or left and/or right rear DAC channels. When the mix signal is added to the output, the gain of the output is automatically adjusted to prevent clipping at high input levels.

The inverse output signal of both CMRR circuits can also be switched to the AUDIOAD\_1 and/or AUDIOAD\_2 and/or AUXAD\_2.

Table 8 Mix volume control

| I <sup>2</sup> C-BUS BIT | OUTPUT MIX GAIN (dB) |  |

|--------------------------|----------------------|--|

| volmix[5:0] (hex)        |                      |  |

| 3F                       | 0                    |  |

| 3B                       | -1.5                 |  |

| 37                       | -3.0                 |  |

| 33                       | -4.5                 |  |

| 2F                       | -6.0                 |  |

| 2B                       | -7.5                 |  |

| 27                       | -9.0                 |  |

| 23                       | -10.5                |  |

| 1F                       | -12.0                |  |

| 1B                       | -13.5                |  |

| I <sup>2</sup> C-BUS BIT |                      |  |

|--------------------------|----------------------|--|

| volmix[5:0] (hex)        | OUTPUT MIX GAIN (dB) |  |

| 17                       | -15.0                |  |

| 13                       | -16.5                |  |

| 0F                       | -18.0                |  |

| 0E                       | -19.5                |  |

| 0D                       | -21.0                |  |

| 0C                       | -22.5                |  |

| 00                       | MUTE                 |  |

The bits volmix[5:2] are binary weighted organized and used for setting the mixer gain from 0 to -18 dB. The selection bits are connected to the mixer in the QSDAC.

The bits volmix[1:0] are also binary weighted organized and connected to the analog front-end.

The MIX signal can be added to all outputs independant of each other.

| Table 9 | Mix output control; note 1 |

|---------|----------------------------|

|---------|----------------------------|

| I <sup>2</sup> C-B | US BIT |     | DAC O | UTPUT |     |

|--------------------|--------|-----|-------|-------|-----|

| BIT                | VALUE  | FL  | FR    | RL    | RR  |

| flm                | 0      | off | Х     | Х     | Х   |

|                    | 1      | on  | Х     | Х     | Х   |

| frm                | 0      | X   | off   | Х     | Х   |

|                    | 1      | X   | on    | Х     | Х   |

| rlm                | 0      | X   | X     | off   | X   |

|                    | 1      | X   | X     | on    | Х   |

| rrm                | 0      | X   | Х     | Х     | off |

|                    | 1      | X   | X     | Х     | on  |

#### Note

1. X = not controlled by this bit.

6.2.5 SUPPLIES AND REFERENCES

6.2.5.1 Reference pins VADCN and VADCP

These pins are used as a negative and positive reference for the AUDIOAD\_1 and AUDIOAD\_2 and the level ADC. These references needs to be "clean".

# SAA7724H

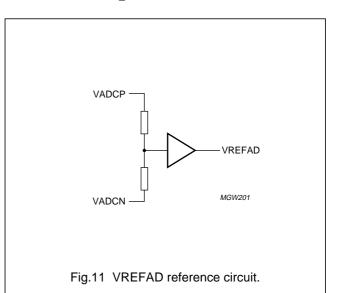

## 6.2.5.2 Reference pin VREFAD

The midref voltage of the ADCs is filtered via this pin. This midref voltage is used for half supply reference of the ADCs. External capacitors (connected to groundplane) prevent crosstalk between the switched capacitor DACs of the internal ADCs and buffers and improves the power supply rejection ratio of all components (see Fig.11).

$$V_{\text{VREFAD}} = \frac{V_{\text{VADCP}} - V_{\text{VADCN}}}{2}$$

#### 6.2.5.3 Analog supply inputs

The analog input circuit has separate power supply  $(V_{DDA1})$  connections to allow maximum filtering. The input stage of every operational amplifier within the analog front-end is supplied by a 3.3 V supply voltage so as to enable a rail-to-rail input signal.

## 6.3 AD decimation paths (DAD)

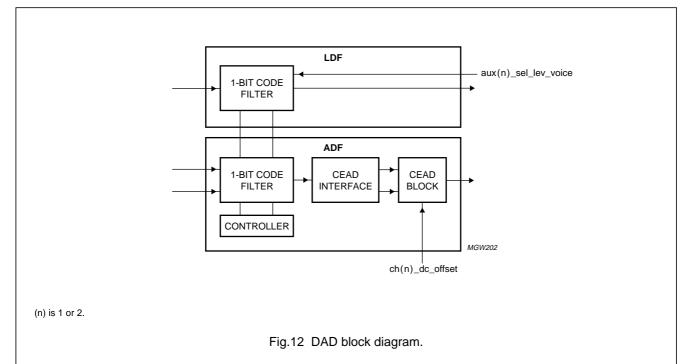

The AD decimation paths for both the level and audio are achieved in the DAD block; (see Fig.12). There are two DAD blocks implemented for the SAA7724H.

Car radio digital signal processor

The DAD block consists of a Level Decimation Filter (LDF) which handles the AUX decimation and an Audio Decimation Filter (ADF) which handles the AUDIO decimation.

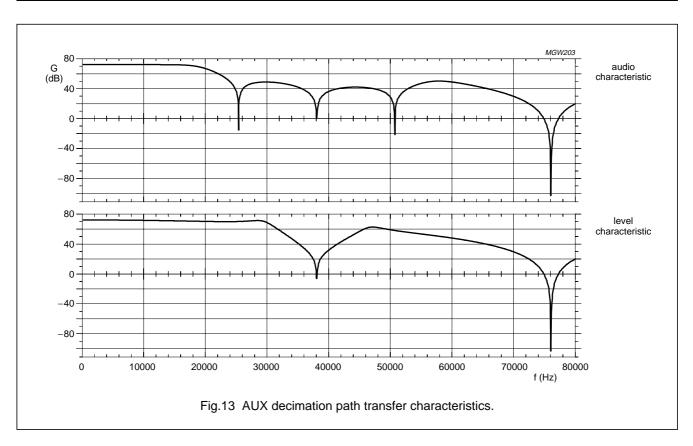

#### 6.3.1 LDF AND AUX DECIMATION PATH

The input signal has a sample frequency of  $128 \times f_s$  and comes from a 1st-order ADC. The first part of the decimation is done using a CIC filter. For the AUX decimating filter a 2nd-order CIC filter is implemented.

A branch is also available from this filter for a signal having a sample frequency of  $8 \times f_s$ . This signal also passes a built-in high-pass filter section to make it adequate for level IAC detection purposes. With a sampling frequency of  $8 \times 42.1875$  kHz the -3 dB point of this filter is at approximately 60 kHz.

The CIC filter decimates the sample frequency by 64. The

new output sample rate is  $2 \times f_s$ . The  $\frac{sin x}{x}$  roll-off of the

CIC filter needs to be compensated for, therefore, a roll-off compensation filter is utilized.

The last stage of the AUX decimation filter is the realization of the appropriate bandwidth characteristic. The bits aux1\_sel\_lev\_voice and aux2\_sel\_lev\_voice selects

between the level characteristic and the audio characteristic for voice input.

The transfer characteristics, level and audio, of the AUX decimation filter are illustrated in Fig.13. It should be noted that the figure corresponds with a 38 kHz sample rate. For the SAA7724H a 42.1875 kHz sample rate is used, the horizontal values need to be scaled with a factor of

# $\frac{42.1875}{38}$

**Remark**: The absolute gain or attenuation of the graphs in Fig.13 has no meaning. The relative levels however have. When bit aux1\_sel\_lev\_voice or aux2\_sel\_lev\_voice is logic 1, the coefficient for audio processing is active. When bit aux1\_sel\_lev\_voice or aux2\_sel\_lev\_voice is logic 0, the coefficient for level processing is selected.

# SAA7724H

#### 6.3.2 ADF AND AUDIO DECIMATION PATH

The input signal has a sample frequency of  $128\times f_s$  and comes from a third order sigma delta ADC. The first step in the decimation process is done by the 1-bit code (CIC) filter. This CIC filter decimates the input sample rate by a factor of 16, which results in a sample rate of  $8\times f_s.$

After the 1-bit code filter, sample rehashing is necessary prior to entering the CEAD block. The CEAD block decimates the audio samples further by a factor of 8, resulting in a sample rate of  $1 \times f_s$ . The overall gain in the pass-band of the decimation filter, including the CIC filter and CEAD block becomes 4.85 dB. A nominal input level of -7.36 dB coming from the ADC will result in a -2.5 dB level after decimation.

The DC filter in the CEAD block is controlled by I<sup>2</sup>C-bus bit ch1\_dc\_offset or ch2\_dc\_offset; see Table 27. There is no power-on reset circuitry implemented. This means that after power-up, all filters will go through a fast transient phase before they reach their steady state behaviour.

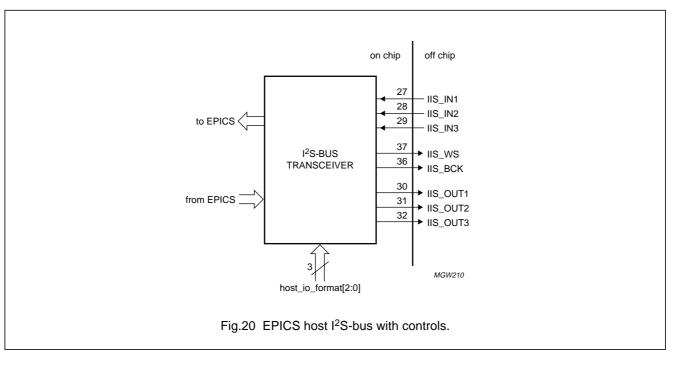

#### 6.4 Digital audio input/output

This section describes the external I<sup>2</sup>S-bus input/output ports, the EPICS host I<sup>2</sup>S-bus port and the SPDIF inputs.

#### 6.4.1 GENERAL

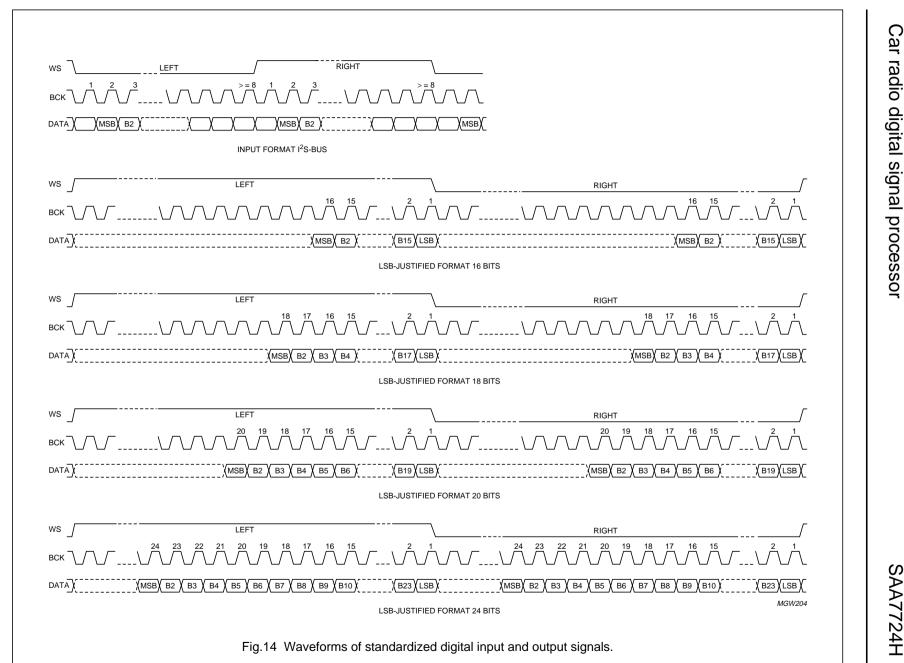

There are two external I<sup>2</sup>S-bus input/output ports available on the circuit, and three host I<sup>2</sup>S-bus ports. The I<sup>2</sup>S-bus inputs and host I<sup>2</sup>S-bus outputs are capable of handling Philips I<sup>2</sup>S-bus, and LSB-justified formats of 16, 18, 20 and 24-bit word sizes. The external I<sup>2</sup>S-bus output ports only support Philips I<sup>2</sup>S-bus. For the general waveforms of the five possible formats see Fig.14. More general information on the Philips I<sup>2</sup>S-bus format is given in Chapter 12.

**Note:** When the applied word length is smaller than 24 bits, the LSB bits will get (internally) a zero value. When the applied word length exceeds 24 bits, the LSBs are skipped.

Philips Semiconductors

27

2003 Nov 18

Preliminary specification

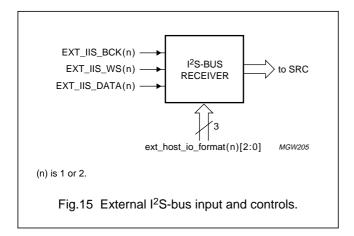

## 6.4.2 EXTERNAL I<sup>2</sup>S-BUS INPUT/OUTPUT PORTS

An I<sup>2</sup>S-bus interface is provided for communication with external digital sources. It is a serial 3-line bus, having one line for data, one line for clock and one line for the word select. For external digital sources the circuit acts as a slave, so the external source is master and supplies the Bit Clock (BCK) and Word Select (WS).

Figure 15 shows the external I<sup>2</sup>S-bus receiver and controls.

Table 10 defines the possible modes that must be set for the  $I^2S$ -bus inputs.

An extra function that is provided is that the EXT\_IIS ports can also be set, as an output, from the Sample Rate Converters (SRC). In this event only the Philips I<sup>2</sup>S-bus format is supported.

## Table 10 External I<sup>2</sup>S-bus input formats

|   | st_io_forma<br>st_io_forma | FORMAT           |                              |

|---|----------------------------|------------------|------------------------------|

| 0 | X <sup>(1)</sup>           | X <sup>(1)</sup> | Philips I <sup>2</sup> S-bus |

| 1 | 0                          | 0                | LSB -justified 16 bits       |

| 1 | 0                          | 1                | LSB-justified 18 bits        |

| 1 | 1                          | 0                | LSB-justified 20 bits        |

| 1 | 1                          | 1                | LSB-justified 24 bits        |

#### Note

1. X = don't care.

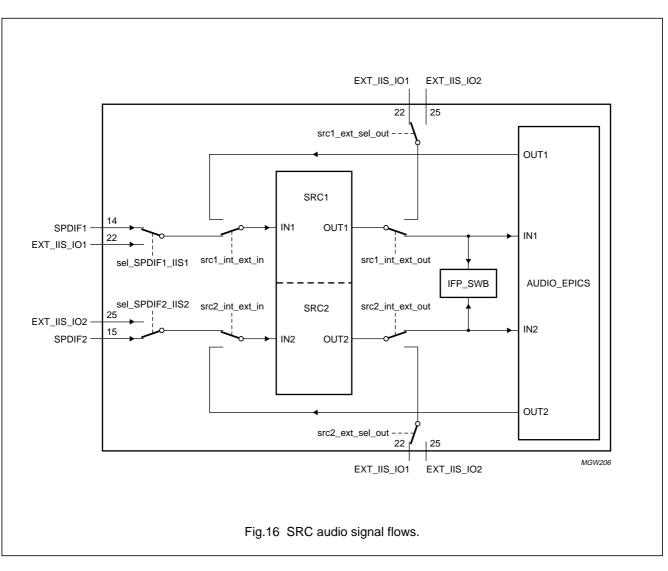

#### 6.4.2.1 SRC audio signal flows

Figure 16 shows the audio signal flow possibilities for the sample rate converters SRC1 and SRC2. The inputs to the SRCs can be either an external source, or an internal signal from the AUDIO\_EPICS.

The outputs from the SRCs can either work as a slave output from an externally connected bus to an external I<sup>2</sup>S-bus Port 1 or 2, or it can convert the internal SAA7724H sample rate directly to the AUDIO\_EPICS and the switchboard in the IFP. If conversion to an external sample rate is selected, the audio signals to the IFPs switchboard and the AUDIO\_EPICS are muted, while their sample rates are maintained at the internal SAA7724H sample rate.

All I/O possibilities of the SRCs can be set by eight independent I<sup>2</sup>C-bus bits. Some selections are conflicting or make no sense. In order to keep as much flexibility as possible there is no detection of conflicting settings, however the circuitry is guaranteed not to cause a hang-up situation.

All audio paths to and from the SRCs are 24 bits wide. Inside the switchboard from the IFP, the audio is always truncated to 16 bits.

# SAA7724H

## 6.4.2.2 Sampling frequency range limitations

The external I<sup>2</sup>S-bus inputs are guaranteed for a continuous 8 kHz to 48 kHz sampling frequency range.

## 6.4.2.3 BCK and WS limitations

The rate at which the I<sup>2</sup>S-bus receivers decode data available to the system, depends on the WS frequency. For normal application only  $1 \times f_s$  is used. The WS duty cycle does not need to be 50 % for any of the applied formats.

#### The BCK is limited to a maximum frequency of $256 \times f_{\text{s}}.$

The lower limit is defined by the number of bits that are required to be sent. For LSB-justified formats the number of BCKs must be at least the number of bits that is selected per channel.

#### 6.4.3 EXTERNAL SPDIF INPUT

A signal can be applied to one or both of the SPDIF inputs that conforms to the IEC 60958 specification.

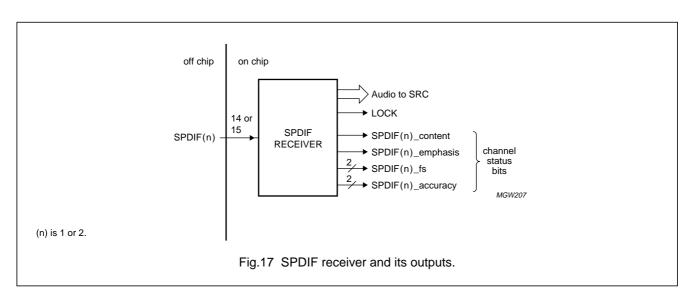

The SPDIF receivers support SPDIF audio data up to 24 bits. Some channel status bits are also decoded and made available to the system.

There is no support for user data decoding, nor availability of the validity bit.

Figure 17 shows the SPDIF receiver and its outputs. The exact meaning of the output bits is given in Table 30. The SPDIF inputs do not have any specific control signals.

# SAA7724H

#### 6.4.3.1 SPDIF input application diagram

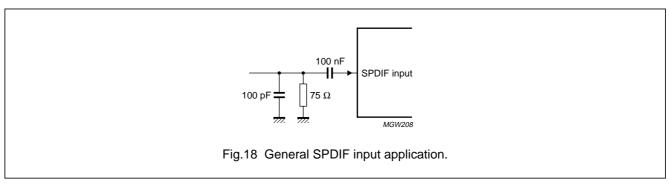

Figure 18 shows the general set-up for an SPDIF input for consumer applications.

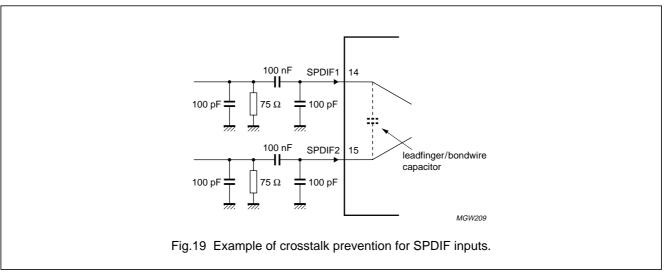

Figure 19 shows an example of how to prevent crosstalk from two adjacent SPDIF inputs, due to the parasitic capacitance from lead finger and bond wires. Therefore extra capacitors are added near the pins.

# SAA7724H

#### 6.4.3.2 Sampling frequency range limitations

The external SPDIF input sample rates are 32, 44.1 and 48 kHz.

The accuracies of the supported standardized sampling frequencies at the SPDIF inputs meets the requirements of Level II accuracy as specified in IEC 60958, being 0.1 %.

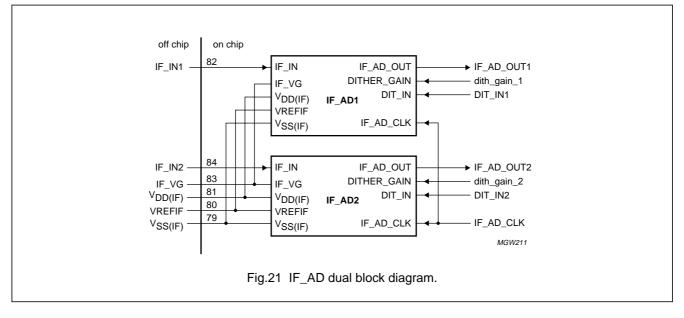

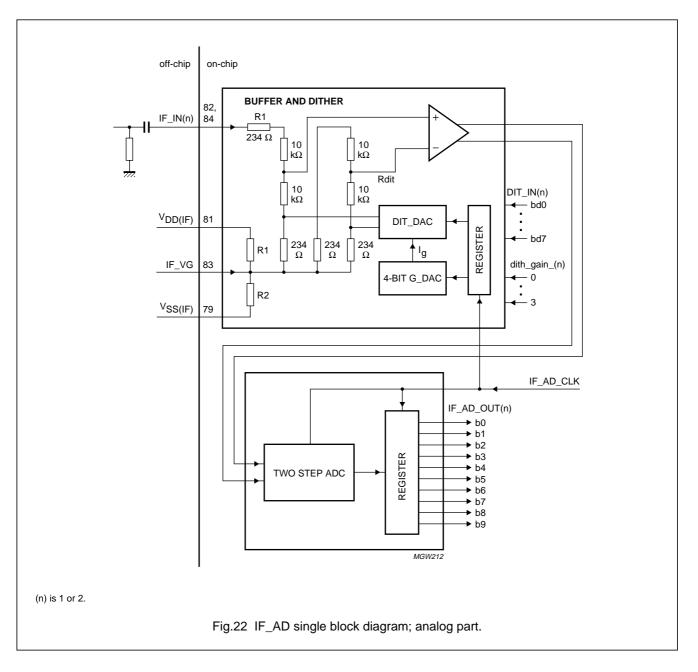

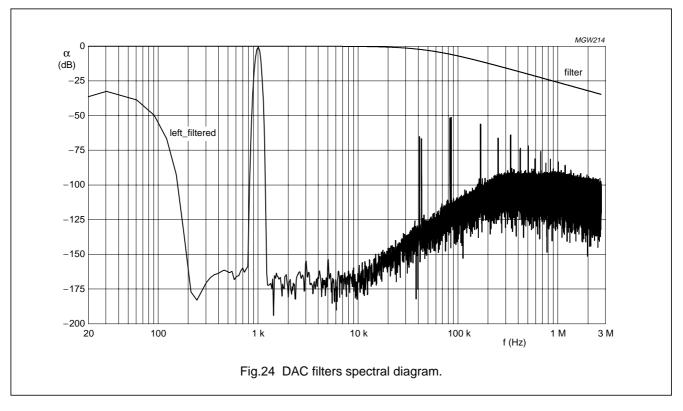

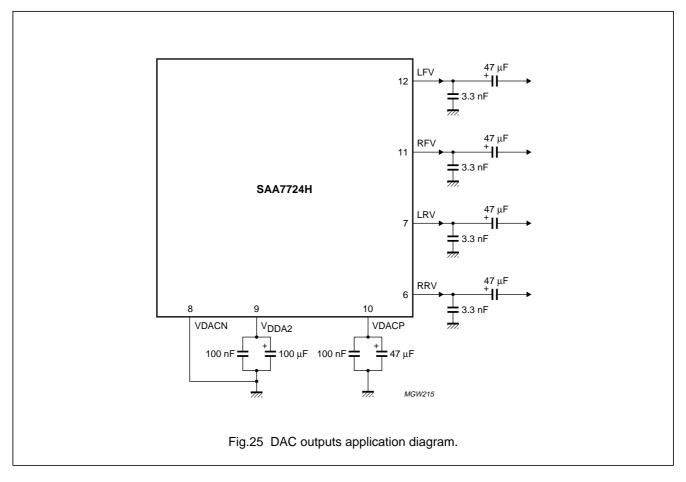

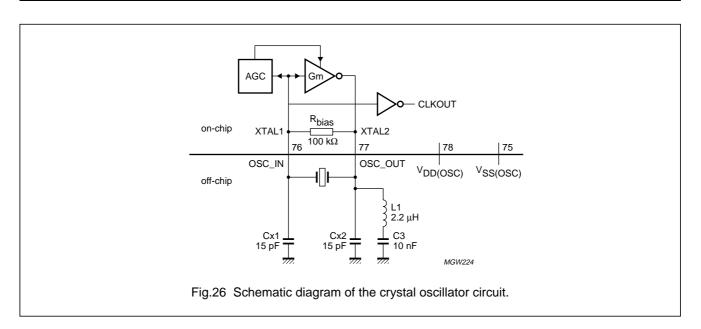

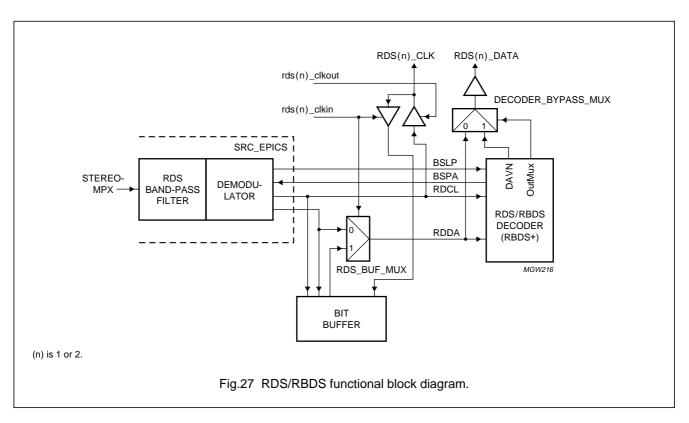

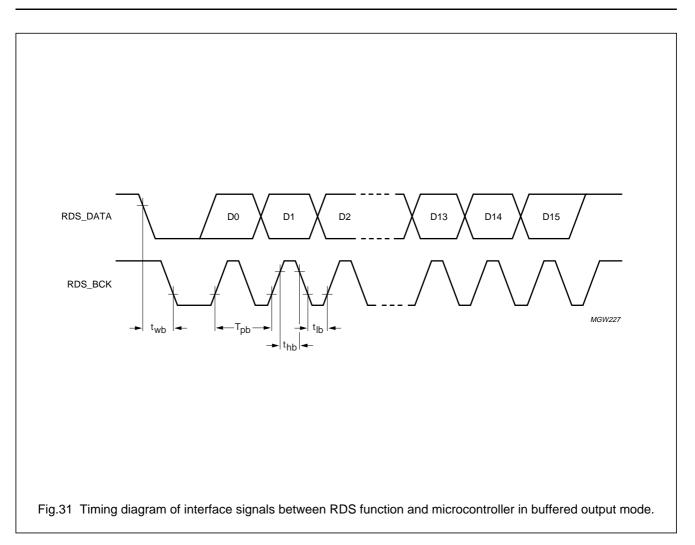

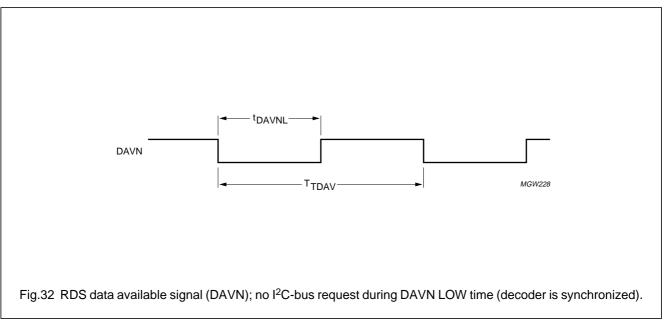

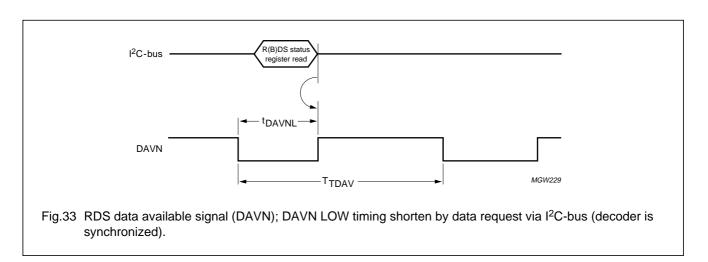

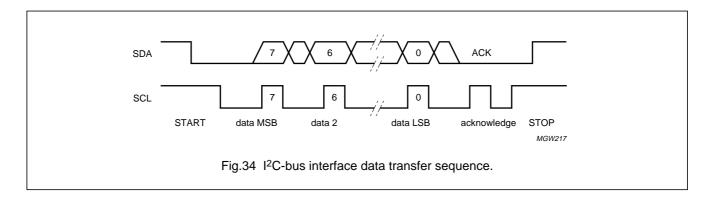

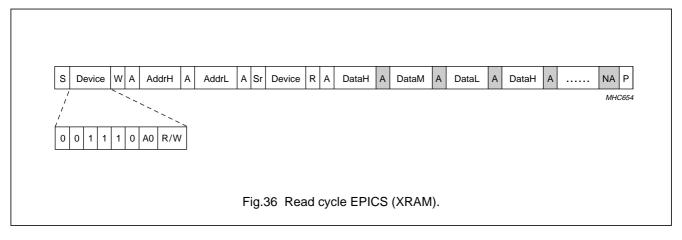

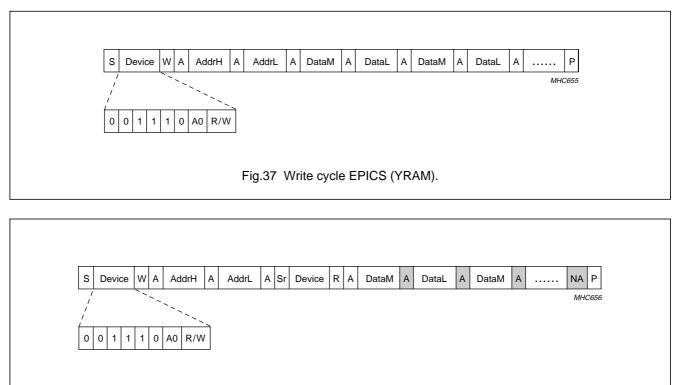

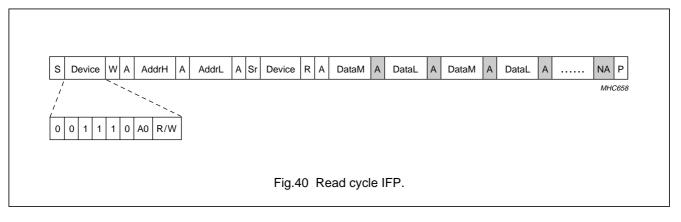

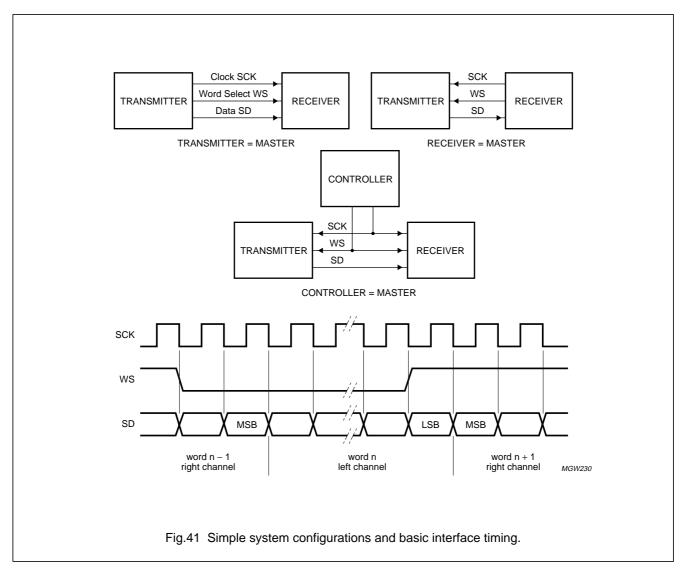

#### 6.4.3.3 Channel status bits